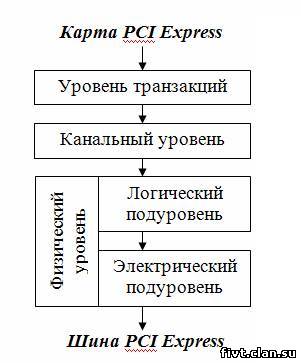

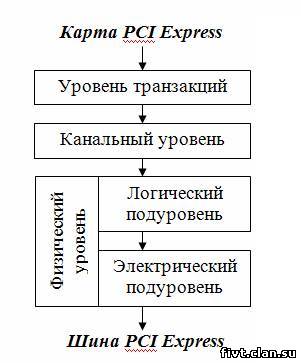

Архитектура PCI Express разделена на три уровня: ● уровень транзакций (Transaction Layer) — верний уровень архитектуры, отвечающий за сборку и разборку транзакционных пакетов TLP (Transaction Layer Packets). Эти пакеты используются для транзакций чтения и записи, а также сообщения о событиях некоторых типов. Каждый пакет TLP имеет уникальный идентификатор, который позволяет направить ответный пакет его отправителю. В TLP используются различные форматы адресации, зависящие от типов транзакций. Пакет может иметь атрибуты отмены слежения за когерентностью NS (No Snoop) и «расслабленной» порядоченности RO (Relaxed Ordering). Каждая транзакция, требующая ответа, выполняется в виде расщепленной (см. PCI-X в главе 2). Уровень транзакций отвечает и за управление потоком, реализованное на основе механизма кредитов;

● канальный уровень (Data Link Layer), промежуточный в стеке, первым делом отвечает за управление связью, обнаружение ошибок и организации повторных передач, до успеха или признания отказа соединения. К пакетам, полученным от уровня транзакций, канальный уровень добавляет номера пакетов и контрольные коды. Канальный уровень и сам является генератором и получателем пакетов DLLP (Data Link Layer Packet), используемых для управления соединением;

● физический уровень изолирует канальный от всех подробностей передачи сигналов. Он состоит из двух субблоков. Логический субблок при передаче выполняет распределение данных по линиям, скремблирование, кодирование по схеме 8B/10B, кадрирование и преобразование в последовательный код. При приеме выполняются обратные действия. Дополнительные символы, обеспечиваемые кодированием 8B/10B, используются для служебной сигнализации. Логический субблок отвечает и за согласование соединения, инициализацию и т. п. Электрический субблок отвечает за электрическое согласование, синхронизацию, обнаружение приемника. Уровневая модель, принятая в PCI Express, позволяет, не затрагивая остальных уровней, заменить физический уровень или его субблоки, когда появятся более эффективные схемы кодирования и сигнализации. Интерфейс между физическим и канальным уровнем зависит от реализации этих компонентов и выбирается их разработчиком. Интерфейс физического уровня четко специфицирован, что обеспечивает возможность соединения устройств разного происхождения. Для тестирования на соответствие электрическим параметрам достаточно подключить устройство PCI Express к специальному тестеру.